The value g = GAMMA * b ± ALPHA is obtained using the three bit times ten bit multiplier (to give the GAMMA * b), and three 74181 arithmetic logic units to make the addition or subtraction.

But, the 74181 ALUs can do more than addition or subtraction...

Here, I've labelled up the rows and columns: discounting duplicates, there are some 38 different arithmetic/logic operations that are possible. The addition of six switches allows any of these different operations to be used:

Hence the thing calculates g = ALU(row,col,A,B), where row and col are the row and column as per the table above, and A = GAMMA * b and B = ALPHA.

So, we have g = ALU(6,2,A,B) = A MINUS B = GAMMA * b - ALPHA; if we set ALPHA = 1 and GAMMA = 2 (with BETA = 20) we get 3.14159265358979323846264338...

But how about something more exotic?

g = ALU(6,0,A,B) = A ⊕ B = GAMMA * b ⊕ ALPHA, where ⊕ is the exclusive or operation.

Setting ALPHA = 1, GAMMA = 1, BETA = 10 and omitting the d = d * b operation (OP#1) (as for the calculation of e), we get

1.543080634815243778477905620757061682601529112365863704737402...

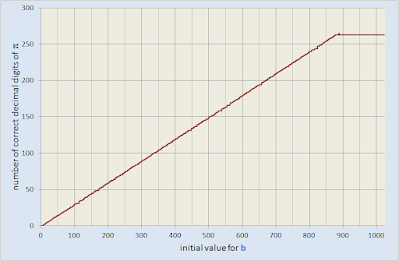

which happens to be cosh(1). The first 2,236 digits of this result are correct. Discovering that this value is cosh(1) wasn't difficult: I just searched for '1.543080634815' on Google!

And there's a lot more of this type of thing...

...another example: ALPHA = 1, BETA = 5, GAMMA = 1, with ALU(1,2) = A | B = GAMMA * b | ALPHA, where | is logical or; operation (OP#1) (again, as for the calculation of e), we get

0.331224981744493362805940652824580844936569932976054216288429...

This equals I1(1) + I0(1) - 3/2 , where I1 and I0 are modified Bessel functions of the first kind. The result from the algorithm is correct to more than 2000 digits.

Showing that the above is indeed the sum of a couple of Bessel functions requires substantially more effort than typing a number into Google. More on this later.

Interestingly, it seems that perhaps all the 38 possible ALU configurations yield 'proper' values, some more 'interesting' than others; I'd naively assumed that the logic operations would not produce anything meaningful, but this appears not to be the case at all.

I'll end this post with another bizarre example:

ALPHA = 15, BETA = 10, GAMMA = 1, with ALU(11,0) = A & B = GAMMA * b & ALPHA, where & is logical and; operation (OP#1) (again, as for the calculation of e), we get

1.718281828461073178906616813933686139831054397588246567510596...

It looks like e - 1 = 1.71828..., but it isn't (the numbers differ at the eleventh decimal place).

Rather, the value appears to be equal to

2246953104077 / 1307674367999

where, even more interestingly, the denominator equals (15! -1). The computed value (1.71828...) and the rational value agree to 672 digits.